MIL-STD-1750A

| بیتها | ۱۶ بیتی |

|---|---|

| تاریخ معرفی | ۱۹۸۰ |

| طرح | CMOS, GaAs, ECL, SoS |

| گونه | RISC |

| کدگذاری | دستورالعمل ۱۶ بیتی |

| افزونهها | FPU, MMU |

| ثبّاتها | |

| هدف اصلی | ۱۶ × ۱۶ بیتی |

| ممیز شناور | مشخصات اختیاری است |

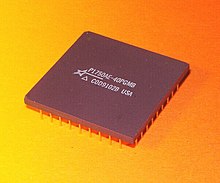

MIL-STD-1750A یک پردازندهٔ ۱۶ بیتی بر پایهٔ معماری مجموعه_دستورالعمل (ISA) است که شامل مولفههای اصلی و اختیاری است؛ که دستورات اختیاری در آن شامل واحد ممیز شناور (FPU) و مدیریت حافظه (MMU) میباشد.[۱][۲] استانداردی که برای 1750A توسط سازمان استانداردهای ارتش آمریکا توزیع شدهاست، شامل نحوهٔ پیادهسازی این ریز پردازنده نمیشود، که منجر گشته نسخههای متفاوتی از این ریز پردازنده توسط شرکتهای مختلف تولید شود.[۳]

در درون 1750A[ویرایش]

طبق استانداردی منتشر شده برای 1750A , این پردازنده از کلمهٔ ۱۶-بیتی پشتیبانی میکند. همچنین در استاندارد یک واحد مدیریت حافظه (به صورت اختیاری) تعریف شدهاست که میتواند با استفاده از ۵۱۲ صفحهٔ رجیسترهای نگاشت از کلمهٔ ۱۶-بیتی (در نظر گرفته شده در فضای I/O) پشتیبانی کند.[۳]

برنامهنویسی[ویرایش]

برنامهنویسی برای این ریز پردازنده معمولاً توسط زبان JOVIAL که یک زبان برنامهنویسی سطح بالا است انجام میشود. این زبان برگرفته از زبان ALGOL 58 است.[۴]

منابع[ویرایش]

- ↑ «نسخه آرشیو شده». بایگانیشده از اصلی در ۲۳ آوریل ۲۰۲۱. دریافتشده در ۱۸ مه ۲۰۲۱. مقدار

|dead-url=deadنامعتبر (کمک) - ↑ https://www.cs.uoregon.edu/Reports/AREA-201902-Pollard.pdf

- ↑ ۳٫۰ ۳٫۱ http://www.mssl.ucl.ac.uk/swift/docs/mil-std-1750a.pdf

- ↑ https://www.avivadirectory.com/Computers-and-Internet/Programming/JOVIAL/