حکاکی یون واکنشی عمیق

حکاکی یون واکنشی عمیق (DRIE) یک فرایند اچ بسیار ناهمسانگرد است که برای ایجاد نفوذ عمیق، سوراخها و ترانشههای شیبدار در ویفرها / بسترها، معمولاً با نسبتهای تصویر بالا استفاده میشود. این برای سیستمهای میکروالکترومکانیکی (MEMS) که به این ویژگیها نیاز دارند، توسعه داده شد، اما همچنین برای حفاری ترانشهها برای خازنهای با چگالی بالا برای DRAM و اخیراً برای ایجاد از طریق vias سیلیکونی (TSVs) در فناوری پیشرفته بستهبندی سطح ویفر سه بعدی استفاده میشود. در DRIE، بستر درون یک راکتور قرار میگیرد و چندین گاز وارد میشود. پلاسما در مخلوط گاز اصابت میکند که مولکولهای گاز را به یون میشکند. یونها به سمت سطح ماده حکاکی شده شتاب میگیرند و با آن واکنش میدهند و عنصر گازی دیگری را تشکیل میدهند. این به عنوان بخش شیمیایی حکاکی یونی فعال شناخته میشود. یک بخش فیزیکی نیز وجود دارد، اگر یونها انرژی کافی داشته باشند، میتوانند بدون واکنش شیمیایی، اتمها را از ماده خارج کنند.

DRIE یک زیر کلاس خاص از RIE است.

دو فناوری اصلی برای DRIE با نرخ بالا وجود دارد: برودتی و بوش، اگرچه فرایند بوش تنها تکنیک تولید شناخته شدهاست. هر دو فرایند بوش و کریو میتوانند دیوارهای ۹۰ درجه (واقعاً عمودی) بسازند، اما اغلب دیوارها کمی مخروطی هستند، به عنوان مثال ۸۸ درجه ("بازگشت") یا ۹۲ درجه ("بازگشت").

مکانیسم دیگر غیرفعال سازی دیواره جانبی: گروههای عاملی SiOx Fy (که از هگزافلوورید گوگرد و گازهای اچ اکسیژن منشأ میگیرند) روی دیوارههای جانبی متراکم میشوند و از آنها در برابر اچ جانبی محافظت میکنند. به عنوان ترکیبی از این فرایندها میتوان ساختارهای عمودی عمیقی ساخت.

فرآیند برودتی

[ویرایش]در Cryogenic-DRIE، ویفر تا ۱۱۰- درجه سانتی گراد (۱۶۳ کلوین) سرد میشود. دمای پایین باعث کند شدن واکنش شیمیایی میشود که منجر به حکاکی ایزوتروپیک میشود. با این حال، یونها به بمباران سطوح رو به بالا ادامه میدهند و آنها را از بین میبرند و روی بسترها در سرمای شدید ترک میخورند، بهعلاوه محصولات جانبی اچ تمایل دارند روی نزدیکترین سطح سرد، یعنی زیرلایه یا الکترود رسوب کنند.

فرایند بوش

[ویرایش]-

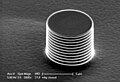

یک ریز ستون سیلیکونی که با استفاده از فرآیند بوش ساخته شدهاست

فرایند بوش، به نام شرکت آلمانی Robert Bosch GmbH که این فرایند را ثبت کردهاست، نامگذاری شدهاست،[۱][۲][۳][۴][۵][۶] همچنین به عنوان اچینگ پالسی یا مولتی پلکس زمانی شناخته میشود، بهطور مکرر برای دستیابی به ساختارهای تقریباً عمودی بین دو حالت متناوب میشود:

- یک اچ پلاسما استاندارد و تقریباً همسانگرد. پلاسما حاوی مقداری یون است که از جهت تقریباً عمودی به ویفر حمله میکند. هگزا فلوراید گوگرد [SF 6] اغلب برای سیلیکون استفاده میشود.

- رسوب یک لایه غیرفعال بی اثر شیمیایی. (به عنوان مثال، گاز منبع Octafluorocyclobutan [C 4 F 8] ماده ای مشابه تفلون تولید میکند).

-

دیواره موجدار ساختار سیلیکونی که با استفاده از فرآیند بوش ایجاد شدهاست.

هر مرحله چند ثانیه طول میکشد. لایه غیرفعال از کل بستر در برابر حملات شیمیایی بیشتر محافظت میکند و از اچ شدن بیشتر جلوگیری میکند. با این حال، در طول مرحله اچینگ، یونهای جهتدار که زیرلایه را بمباران میکنند، به لایه غیرفعال سازی در پایین ترانشه (اما نه در امتداد طرفین) حمله میکنند. آنها با آن برخورد میکنند و آن را پاشیده میکنند و بستر را در معرض مواد شیمیایی قرار میدهند.

این مراحل اچ/رسوب بارها تکرار میشوند و در نتیجه تعداد زیادی از مراحل اچ همسانگرد بسیار کوچک فقط در پایین حفرههای اچشده انجام میشوند. برای اچ کردن از طریق ویفر سیلیکونی ۰٫۵ میلیمتر، فرایند دو فازی باعث میشود که دیوارههای جانبی با دامنهای در حدود ۱۰۰ تا ۵۰۰ نانومتر موجدار شوند. زمان چرخه را میتوان تنظیم کرد: چرخههای کوتاه دیوارههای صاف تری را ایجاد میکنند و چرخههای طولانی نرخ اچ بالاتری را ایجاد میکنند.

برنامههای کاربردی

[ویرایش]«عمق» RIE به کاربرد بستگی دارد:

- در مدارهای حافظه DRAM، ترانشههای خازن ممکن است ۱۰ تا ۲۰ میکرومتر عمق داشته باشد

- در MEMS, DRIE برای هر چیزی از چند میکرومتر تا ۰٫۵ میلیمتر استفاده میشود

- در قالبسازی تراشههای نامنظم، DRIE با یک ماسک ترکیبی نرم/سخت جدید برای دستیابی به حکاکی زیر ۱ میلیمتری برای تقسیم قالبهای سیلیکونی به قطعات لگو مانند با اشکال نامنظم استفاده میشود.[۷][۸][۹]

- در الکترونیک انعطافپذیر، DRIE برای انعطافپذیر ساختن دستگاههای CMOS یکپارچه سنتی با کاهش ضخامت بسترهای سیلیکونی به چند تا دهها میکرومتر استفاده میشود.[۱۰][۱۱][۱۲][۱۳][۱۴][۱۵]

آنچه DRIE را از RIE متمایز میکند عمق اچ است: عمق اچ عملی برای RIE (همانطور که در تولید آی سی استفاده میشود) به حدود ۱۰ میکرومتر محدود میشود. در حالی که DRIE میتواند ویژگیهای بسیار بزرگتر، از ۲۰ میکرومتر تا ۶۰۰ میکرومتر یا بیشتر در در دقیقه را حک کند.

DRIE شیشه به قدرت پلاسمای بالایی نیاز دارد که یافتن مواد ماسک مناسب برای حکاکی عمیق را دشوار میکند. پلی سیلیکون و نیکل برای ۱۰–۵۰ میکرومتر استفاده میشود اعماق حکاکی شده در DRIE پلیمرها، فرایند بوش با مراحل متناوب اچینگ SF 6 و غیرفعال سازی C 4 F 8 انجام میشود. ماسکهای فلزی (Si [تا ۸۰۰ میکرومتر]، InP [تا ۴۰ میکرومتر] یا شیشه [تا ۱۲ میکرومتر)) را میتوان استفاده کرد، اما استفاده از آنها گران است زیرا چندین مرحله عکس و رسوب اضافی همیشه مورد نیاز است. ماسکهای فلزی در بسترهای مختلف ضروری نیستند در صورتی ضروری هستند که استفاده از مقاومتهای منفی تقویت شده شیمیایی باشد.

کاشت یون گالیوم را میتوان به عنوان ماسک اچ در cryo-DRIE استفاده کرد. فرایند ترکیبی نانوساخت پرتو یون متمرکز و کرایو-DRIE برای اولین بار توسط N Chekurov و همکاران در مقاله خود «ساخت نانوساختارهای سیلیکونی با کاشت محلی گالیوم و اچ کردن یون واکنشی عمیق برودتی» گزارش شدهاست.[۱۶]

ماشین آلات دقیق

[ویرایش]DRIE امکان استفاده از اجزای مکانیکی سیلیکونی را در ساعتهای مچی پیشرفته فراهم کردهاست. به گفته یک مهندس در Cartier، «هیچ محدودیتی برای اشکال هندسی با DRIE وجود ندارد.»[۱۷] با DRIE میتوان نسبت ابعاد ۳۰ یا بیشتر را بدست آورد،[۱۸] به این معنی که یک سطح را میتوان با یک ترانشه با دیواره عمودی ۳۰ برابر عمیقتر از عرض آن حک کرد.

این باعث شدهاست که اجزای سیلیکونی جایگزین برخی از قطعاتی که معمولاً از فولاد هستند، مانند فنر مو، شوند. سیلیکون سبکتر و سختتر از فولاد است، که مزایایی دارد اما فرایند تولید را چالشبرانگیزتر میکند.

منابع

[ویرایش]- ↑ Basic Bosch process patent application

- ↑ Improved Bosch process patent application

- ↑ Bosch process "Parameter Ramping" patent application

- ↑ Method of anisotropically etching silicon

- ↑ Method for anisotropic etching of silicon

- ↑ Method of anisotropic etching of silicon

- ↑ Ghoneim, Mohamed; Hussain, Muhammad (1 February 2017). "Highly Manufacturable Deep (Sub-Millimeter) Etching Enabled High Aspect Ratio Complex Geometry Lego-Like Silicon Electronics" (PDF). Small. 13 (16): 1601801. doi:10.1002/smll.201601801. hdl:10754/622865. PMID 28145623.

- ↑ Mendis, Lakshini (14 February 2017). "Lego-like Electronics". Nature Middle East. doi:10.1038/nmiddleeast.2017.34.

- ↑ Berger, Michael (6 February 2017). "Lego like silicon electronics fabricated with hybrid etching masks". Nanowerk.

- ↑ Ghoneim, Mohamed; Alfaraj, Nasir; Torres-Sevilla, Galo; Fahad, Hossain; Hussain, Muhammad (July 2016). "Out-of-Plane Strain Effects on Physically Flexible FinFET CMOS". IEEE Transactions on Electron Devices. 63 (7): 2657–2664

- ↑ Ghoneim, Mohamed T.; Hussain, Muhammad M. (23 July 2015). "Review on physically flexible nonvolatile memory for internet of everything electronics". Electronics. 4 (3): 424–479. arXiv:1606.08404. doi:10.3390/electronics4030424.

- ↑ Ghoneim, Mohamed T. ; Hussain, Muhammad M. (3 August 2015). "Study of harsh environment operation of flexible ferroelectric memory integrated with PZT and silicon fabric" (PDF). Applied Physics Letters. 107 (5): 052904. Bibcode:2015ApPhL.107e2904G. doi:10.1063/1.4927913. hdl:10754/565819.

- ↑ Ghoneim, Mohamed T.; Rojas, Jhonathan P.; Young, Chadwin D.; Bersuker, Gennadi; Hussain, Muhammad M. (26 November 2014). "Electrical Analysis of High Dielectric Constant Insulator and Metal Gate Metal Oxide Semiconductor Capacitors on Flexible Bulk Mono-Crystalline Silicon". IEEE Transactions on Reliability. 64 (2): 579–585. doi:10.1109/TR.2014.2371054.

- ↑ Ghoneim, Mohamed T.; Zidan, Mohammed A.; Alnassar, Mohammed Y.; Hanna, Amir N.; Kosel, Jurgen; Salama, Khaled N.; Hussain, Muhammad (15 June 2015). "Flexible Electronics: Thin PZT-Based Ferroelectric Capacitors on Flexible Silicon for Nonvolatile Memory Applications". Advanced Electronic Materials. 1 (6): 1500045. doi:10.1002/aelm.201500045.

- ↑ Ghoneim, Mohamed T. ; Kutbee, Arwa; Ghodsi, Farzan; Bersuker, G. ; Hussain, Muhammad M. (9 June 2014). "Mechanical anomaly impact on metal-oxide-semiconductor capacitors on flexible silicon fabric" (PDF). Applied Physics Letters. 104 (23): 234104. Bibcode:2014ApPhL.104w4104G. doi:10.1063/1.4882647. hdl:10754/552155.

- ↑ Chekurov, N; Grigoras, K; et al. (11 February 2009). "The fabrication of silicon nanostructures by local gallium implantation and cryogenic deep reactive ion etching". Nanotechnology. 20 (6): 065307. doi:10.1088/0957-4484/20/6/065307. PMID 19417383.

- ↑ Kolesnikov-Jessop, Sonia (23 November 2012). "Precise Future of Silicon Parts Still Being Debated". The New York Times. New York.

- ↑ Yeom, Junghoon; Wu, Yan; Selby, John C.; Shannon, Mark A. (2005). "Maximum achievable aspect ratio in deep reactive ion etching of silicon due to aspect ratio dependent transport and the microloading effect". Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures. American Vacuum Society. 23 (6): 2319. Bibcode:2005JVSTB..23.2319Y. doi:10.1116/1.2101678. ISSN 0734-211X.