اینتل ۸۲۵۹

اینتل ۸۲۵۹ یک کنترل گر وقفه برنامه پذیر (PIC) است که برای ریزپردازندههای اینتل ۸۰۸۵ و اینتل ۸۰۸۶ طراحی شدهاست. در ابتدا قطعه اولیه ۸۲۵۹ بود، سپس نسخه بعدی با پسوند A که با پردازنده ۸۰۸۶ یا 8088 سازگار بود. ۸۲۵۹ چندین منبع ورودی وقفه را به عنوان یک خروجی وقفه به ریزپردازنده میزبان ادغام میکند و سطوح وقفه موجود در یک سیستم را فراتر از یک یا دو سطح موجود در تراشه پردازنده گسترش میدهد. 8259A کنترلکننده وقفه برای گذرگاه ISA در IBM PC اوریجینال و IBM PC AT بود.

۸۲۵۹ به عنوان بخشی از خانواده MCS 85 اینتل در سال ۱۹۷۶ معرفی شد. 8259A در PC اصلی که در سال ۱۹۸۱ معرفی شد گنجانده شد و در PC/XT که در ۱۹۸۳ معرفی شد هم حفظ شد. 8259A دومی نیز با معرفی PC/AT اضافه شد. ۸۲۵۹ با معماری APIC اینتل از زمان معرفی آن در رایانههای شخصی چند پردازنده ای متقارن، همزیستی داشته است. رایانههای شخصی مدرن شروع به حذف تدریجی 8259A به نفع معماری APIC اینتل کردهاند. با این حال، در حالی که دیگر یک تراشه جداگانه نیست، رابط 8259A همچنان توسط پلتفرم Controller Hub و چیپ ست Southbridge در مادربردهای مدرن x86 ارائه میشود.[۱]

توضیح عملکرد

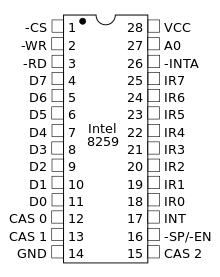

[ویرایش]پینهای سیگنال اصلی روی یک ۸۲۵۹ به شرح زیر است:

هشت خط درخواست ورودی وقفه به نام IRQ0 تا IRQ7، یک خط خروجی درخواست وقفه به نام INTR، خط تأیید وقفه به نام INTA,

D0 تا D7 برای ارتباط سطح وقفه یا آفست بردار. سایر اتصالات شامل CAS0 تا CAS2 برای زنجیروار کردن ۸۲۵۹ها میباشد.

تا 8 slave۸۲۵۹ ممکن است به یک Master 8259 برای ارائه حداکثر 64 IRQ وصل شوند. ۸۲۵۹ها با اتصال خط INT یک slave 8259 به خط IRQ یک master 8259 متصل میشوند.

سه رجیستر وجود دارد، یک ثبت نقاب وقفه (IMR)، یک ثبت درخواست وقفه (IRR) و یک (ISR). IRR یک پوشش از وقفههای فعلی را که در انتظار تأیید هستند حفظ میکند. ISR پوششی از وقفههایی که در انتظار EOI هستند را حفظ میکند. و IMR پوششی از وقفههایی را که نباید برایشان تأییدیه ارسال شود، حفظ میکند.

عملیات پایان وقفه (EOI) از EOI اختصاصی، EOI غیر اختصاصی و EOI اتومات پشتیبانی میکند. یک EOI اختصاصی سطح IRQ ای که در ISR تأیید میکرده را مشخص میکند. یک EOI غیر اختصاصی سطح IRQ را در ISR بازنشانی میکند.

Auto-EOI سطح IRQ را در ISR بلافاصله پس از تأیید وقفه بازنشانی میکند.

هردو حالت برانگیزی وقفه لبه و سطح توسط 8259A پشتیبانی میشوند. اولویت ثابت و حالتهای اولویت چرخشی نیز پشتیبانی میشوند.

میتوان ۸۲۵۹ را برای کار با ۸۰۸۰/۸۰۸۵ یا ۸۰۸۶/۸۰۸۸ پیکربندی کرد و تغییر داد. روی ۸۰۸۶/۸۰۸۸، کنترلکننده وقفه زمانی که یک وقفه رخ میدهد، یک عدد وقفه در گذرگاه داده ارائه میدهد. چرخه وقفه ۸۰۸۰/۸۰۸۵ سه بایت در گذرگاه داده صادر میکند (مطابق با یک دستور CALL در مجموعه دستورالعمل ۸۰۸۰/۸۰۸۵).

8259A عملکردهای بیشتری را در مقایسه با ۸۲۵۹ (به ویژه حالت بافر و حالت فعال سطح) ارائه میدهد و با حالات بالاتر سازگار است.

ملاحظات حین برنامهنویسی

[ویرایش]داس و ویندوز

[ویرایش]

برنامهنویسی یک ۸۲۵۹ در قالبDOS و مایکروسافت ویندوز، برای دلیل سازگاری با نسخههای قبلی، مشکلات گیج کننده ای را به وجود آورده است که به قدمت PC اصلی معرفی شده در سال ۱۹۸۱ باز میگردد.

مشکل اول تقریباً ریشه مشکل دوم است.

انتظار میرود درایورهای دستگاه DOS پس از اتمام سرویس دستگاه خود، EOI غیر اختصاصی را به ۸۲۵۹ها ارسال کنند. این از استفاده از هر یک از حالتهای دیگر EOI 8259 در DOS جلوگیری میکند و تمایز بین وقفههای دستگاهی که از Master 8259 به Slave 8259 تغییر مسیر داده شدهاند را از بین میبرد.

موضوع دوم به استفاده از IRQ2 و IRQ9 از معرفی یک slave 8259 در PC/AT میپردازد.

خروجی INT یک slave 8259 به IR2 master متصل است. خط IRQ2

ISA، که در ابتدا به این IR2 متصل بود، به IR1 برده تغییر مسیر پیدا کرده؛ بنابراین خط قدیمی IRQ2 اکنون IRQ9 را در CPU تولید میکند. برای اجازه دادن به سازگاری با درایورهای دستگاه DOS که هنوز برای IRQ2 تنظیم شدهاند، یک کنترلر توسط BIOS برای IRQ9 نصب شدهاست که وقفهها را به کنترلکننده اصلی IRQ2 هدایت میکند.

در رایانه شخصی، BIOS (و بنابراین DOS) بهطور سنتی درخواستهای وقفه اصلی 8259 (IRQ0-IRQ7) را برای وقفه بردار آفست 8 (INT08-INT0F) و درخواستهای وقفه ۸۲۵۹ برده (در PC/AT و جدیدتر) ترسیم میکند تا بردار افست 112 (INT70-INT77)را قطع کند. این کار با وجود ۳۲ بردار وقفه اول (INT00-INT1F) انجام میشد که توسط پردازنده برای کیسهای استثنا داخلی رزرو شده بود (این امر به دلایلی برای طراحی رایانه شخصی نادیده گرفته شد). به دلیل بردارهای رزرو شده برای استثناها، اکثر سیستم عاملهای دیگر (حداقل اصلی) 8259 IRQ ها (در صورت استفاده در یک پلت فرم) را به یک افست پایه بردار وقفه دیگر ترسیم میکنند.

سایر سیستم عاملها

[ویرایش]از آنجایی که اکثر سیستم عاملهای دیگر امکان تغییر در انتظارات درایور دستگاه را فراهم میکنند، سایر حالتهای عملکرد ۸۲۵۹، مانند Auto-EOI، ممکن است استفاده شوند. این امر به ویژه برای سختافزار مدرن x86 (که در آن ممکن است زمان قابلتوجهی برای تأخیر فضای آدرس ورودی/خروجی هنگام برقراری ارتباط با ۸۲۵۹ صرف شود) مهم است. این همچنین تعدادی بهینهسازی دیگر را در همگام سازی، مانند بخشهای بحرانی، در یک سیستم چند پردازنده ای x86 با 8259s امکانپذیر میکند.

حالتهای راهاندازی لبه و سطح

[ویرایش]از آنجایی که گذرگاه ISA از وقفههای راهاندازی سطح پشتیبانی نمیکند، حالت راهاندازی سطح ممکن است برای وقفههای متصل به دستگاههای ISA استفاده نشود. این بدان معناست که در PC/XT, PC/AT، و سیستمهای سازگار، ۸۲۵۹ باید برای حالت edge triggered (راه اندازی لبه) برنامهریزی شود. در سیستمهای MCA، دستگاهها از وقفههای راهاندازی سطح استفاده میکنند و کنترلکننده وقفه برای همیشه در حالت راهاندازی در سطح کار میکند. در سیستمهای جدیدتر EISA, PCI، و سیستمهای بعدی، Edge/Level Control Registers (ELCRs),

حالت را در هر خط IRQ کنترل میکنند، که عملاً حالت ۸۲۵۹ را برای چنین سیستمهایی با ISAها نامربوط میکند. ELCR در هنگام راه اندازی سیستم برای عملکرد صحیح توسط بایوس برنامهریزی میشود.

ELCRها در فضای آدرس 0x4d0 و 0x4d1 ورودی/خروجی x86 قرار دارند. عرض آنها ۸ بیت است که هر بیت مربوط به یک IRQ از ۸۲۵۹ها است. هنگامی که یک بیت تنظیم میشود، IRQ در حالت راه اندازی سطح است. در غیر این صورت، IRQ در حالت تحریک لبه است.

وقفههای جعلی

[ویرایش]۸۲۵۹ در پاسخ به بعضی از حالات وقفههای جعلی تولید میکند.

اولین مورد، یک خط IRQ است که قبل از تأیید آن از بین رفتهاست. این ممکن است به دلیل نویز در خطوط IRQ رخ دهد. در حالت تحریک لبه، نویز باید خط را به مدت 100 ns در حالت کم نگه دارد. هنگامی که نویز کاهش مییابد، یک مقاومت کششی خط IRQ را به بالا برمیگرداند و در نتیجه یک وقفه کاذب ایجاد میکند. در حالت تحریک سطح، نویز ممکن است باعث افزایش سطح سیگنال در خط INTR سیستم شود. اگر سیستم یک درخواست تأیید ارسال کند، ۸۲۵۹ چیزی برای حل کردن ندارد و بنابراین در پاسخ یک IRQ7 ارسال میکند. این مورد IRQ7های جعلی تولید میکند.

مورد مشابهی ممکن است زمانی رخ دهد که ۸۲۵۹ بدون پوشش شوند و de-assertion ورودی IRQ به درستی هماهنگ نشده باشد. در بسیاری از سیستمها، ورودی IRQ با نوشتن یک I/O از بین میرود و پردازنده منتظر نمیماند تا نوشتن به دستگاه I/O برسد. اگر پردازنده به کار خود ادامه دهد و 8259 IRQ را قبل از اینکه ورودی IRQ غیرفعال شود، باز کند، ۸۲۵۹ دوباره INTR را تأیید میکند. تا زمانی که پردازنده این INTR را تشخیص دهد و تأییدیه خواندن IRQ از ۸۲۵۹ را صادر کند، ممکن است ورودی IRQ خالی شود و ۸۲۵۹ یک IRQ7 جعلی را برمیگرداند.

دوم این است که IRQ2 مربوط به ۸۲۵۹ مستر زمانی فعال است که خطوط IRQ 8259 برده در لبه سقوط یک تأیید وقفه غیرفعال هستند. این مورد دوم IRQ15های جعلی تولید میکند، اما به ندرت اتفاق میفتد.

PC/XT و PC/AT

[ویرایش]سیستم PC/XT ISA دارای یک کنترلر ۸۲۵۹ است، در حالی که سیستمهای PC/AT و سیستمهای جدیدتر دارای دو کنترلرmaster و slave از سری ۸۲۵۹ بودند. IRQ0 تا IRQ7 خطوط وقفه ۸۲۵۹ مستر هستند، در حالی که IRQ8 تا IRQ15 خطوط وقفه ۸۲۵۹ برده(slave) هستند. برچسبهای روی پینهای یک ۸۲۵۹ از IR0 تا IR7 هستند. IRQ0 تا IRQ15 نام خطوط ISA است که ۸۲۵۹ها به آنها متصل است.

انواع

[ویرایش]| شماره مدل | فن آوری | محدوده دما | تاریخ انتشار | قیمت (دلار آمریکا)[list ۱] |

|---|---|---|---|---|

| ID8259 | -۴۰ درجه سانتی گراد تا +۸۵ درجه سانتی گراد[۲] | مارس/آوریل 1979[۳] | ۲۳٫۱۵ دلار | |

| M8259 | نظامی | مارس/آوریل 1979[۴] | ۹۵٫۰۰ دلار | |

| 82C59A[۵] | CMOS | جولای/آگوست ۱۹۸۴ |

- ↑ In quantities of 100 and up

جستارهای وابسته

[ویرایش]- کنترلکننده وقفه قابل برنامهریزی پیشرفته (APIC)

- IF (پرچم x86)

- کنترلکننده وقفه

- تأخیر را قطع کنید

- وقفه غیرقابل پوشش (NMI)

- کنترلکننده وقفه قابل برنامهریزی (PIC)

منابع

[ویرایش]- ↑ http://pdf.datasheetcatalog.com/datasheet/Intel/mXvqwzr.pdf

- ↑ Intel Corporation, "8086 Available for industrial environment", Intel Preview Special Issue: 16-Bit Solutions, May/June 1980, Page 29

- ↑ Intel Corporation, "Microcomputer Component: New industrial grade product line answers the demand for high-reliability components to operate in industrial applications.", Intel Preview, March/April 1979, Pg. 11

- ↑ Intel Corporation, "Military Products: Intel marches on!", Intel Preview, March/April 1979, Pg. 19

- ↑ Intel Corporation, "NewsBit: Intel Licenses Oki on CMOS Version of Several Products", Solutions, July/August 1984, Page 1.

- گیلو، فرانک ون. کامپیوتر بدون سند AW Developers Press، ۱۹۹۷.شابک ۰-۲۰۱-۴۷۹۵۰-۸

- مک گیورن، جوزف. طراحی سیستم کامپیوتر مبتنی بر وقفه. آنابوکز، ۱۹۹۸.شابک ۰−۹۲۹۳۹۲−۵۰−۷شابک 0-929392-50-7

- مرجع فنی IBM Personal System/2 Hardware Interface - Architectures. IBM، 1990. IBM Publication 84F8933